To the Graduate Council:

I am submitting herewith a thesis written by Adam Robert Miller entitled "Development and Verification of Parameterized Digital Signal Processing Macros for Microelectronic Systems." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

|                               | D.W. Bouldin                  |

|-------------------------------|-------------------------------|

|                               | D.W. Bouldin, Major Professor |

|                               |                               |

|                               |                               |

|                               |                               |

| We have read this thesis      |                               |

| and recommend its acceptance: |                               |

|                               |                               |

| Gregory D. Peterson           |                               |

|                               |                               |

| Chandra Tan                   |                               |

|                               | Accepted for the Council:     |

|                               | •                             |

|                               | Anne Mayhew                   |

|                               | Vice Provost and Dean of      |

|                               | Graduate Studies              |

(Original signatures on file with official student records)

# Development and Verification of Parameterized Digital Signal Processing Macros for Microelectronic Systems

A Thesis

Presented for the

Master of Science

The University of Tennessee, Knoxville

Adam Robert Miller August, 2003

# Acknowledgments

First, I would like to thank Dr. Don Bouldin for providing me with the opportunity to do this research. This research reinforced the teachings of my graduate classes, and in most cases went more in-depth on some of the topics and ideas. Secondly, I would like to thank Dr. Chandra Tan and Mr. Fuat Karakaya for assisting me with my research. Without Dr. Tan's knowledge of the intricacies of the software tools involved, a lot of the development time would have taken longer, if it was able to be done at all. Thirdly, I would like to thank the Electrical and Computer Engineering Department at the University of Tennessee for supporting me with a Graduate Teaching Assistantship until I was able to transition into this research project.

Most importantly, I would like to thank my wife Lara for her support. Without her, I do not know if I would have gone into the Master's Degree program in the first place. It was with her support and understanding that I was able to complete this thesis.

This work was partially sponsored by the Defense Advanced Research Projects Agency and the Air Force Research Laboratory under agreement F30602-01-2-0562.

## **Abstract**

Digital system design is a broad field that is growing every day. As technology grows, the complexity of systems grows also, which leads to longer design times. A Design-for-reuse policy can decrease design time by building flexibility into designs as they are created. By creating parameterized macros, they are more likely to be reused. Verifying the capabilities of macros is also important, and testing should be incorporated into each step of the design process. In this thesis, designing parameterized macros is discussed, with a Complex Fast Fourier Transform presented as an example of a complex algorithm, and three different Rounder blocks as examples of simple macros. Each Rounder was tested successfully, instantiating one of the Rounders with several different configurations. The Fast Fourier Transform macro was simulated successfully to Post-layout Simulation for one set of parameters, and for several sets was simulated in the Pre-synthesis step. The Fast Fourier Transform macro was fabricated using a TSMC 180nm process and verified to be working correctly.

# **Table of Contents**

| Chap | oter     |                |                                               | Page |  |  |

|------|----------|----------------|-----------------------------------------------|------|--|--|

| 1.   | Intro    | duction        |                                               | 1    |  |  |

| 2.   | Back     | Background 3   |                                               |      |  |  |

|      | 2.1      | _              | and Design Flow                               |      |  |  |

|      | 2.2      |                | 1-for-Reuse                                   |      |  |  |

|      | 2.3      | _              |                                               |      |  |  |

|      |          | 2.3.1          | Overview                                      |      |  |  |

|      |          | 2.3.2          | The Fast Fourier Transform                    |      |  |  |

|      |          | 2.3.3          | Rounding                                      |      |  |  |

|      | 2.4      | Verific        | cation                                        |      |  |  |

|      |          | 2.4.1          | Overview                                      | 11   |  |  |

|      |          | 2.4.2          | Simulation Types                              |      |  |  |

|      |          | 2.4.3          | Testing                                       | 13   |  |  |

| 3.   | Impl     | Implementation |                                               |      |  |  |

| Σ.   | 3.1      |                | lers                                          |      |  |  |

|      |          | 3.1.1          | Fixed Rounder                                 |      |  |  |

|      |          | 3.1.2          | Configurable Rounder                          |      |  |  |

|      |          | 3.1.3          | Output Gain Stage                             |      |  |  |

|      | 3.2      |                |                                               |      |  |  |

|      |          | 3.2.1          | Shift Registers, Adders, and Subtract Modules |      |  |  |

|      |          | 3.2.2          | Butterfly Types                               |      |  |  |

|      |          | 3.2.3          | Complex Multiplier                            |      |  |  |

|      |          | 3.2.4          | Twiddle Factors                               |      |  |  |

|      |          | 3.2.5          | Control Logic                                 |      |  |  |

|      |          | 3.2.6          | Structure                                     |      |  |  |

|      |          | 3.2.7          | Test Bench                                    | 31   |  |  |

| 4.   | Resu     | Results        |                                               |      |  |  |

|      | 4.1      |                | lers                                          |      |  |  |

|      |          | 4.1.1          | Fixed Rounder                                 |      |  |  |

|      |          | 4.1.2          | Configurable Rounder                          |      |  |  |

|      |          | 4.1.3          | Output Gain Stage                             |      |  |  |

|      | 4.2      | FFT R          | esults                                        |      |  |  |

|      |          | 4.2.1          | MATLAB                                        |      |  |  |

|      |          | 4.2.2          | Pre-synthesis and Pre-layout                  |      |  |  |

|      |          | 4.2.3          | Layout and Post-layout                        |      |  |  |

|      |          | 4.2.4          | Hardware Testing.                             |      |  |  |

|      |          | 4.2.4          | FFT Flexibility                               | 44   |  |  |

| 5.   | Conc     | clusions a     | and Future Work                               | 48   |  |  |

| List | of Refer | ences          |                                               | 49   |  |  |

|      |          |                |                                               |      |  |  |

| Vita |          |                |                                               | 106  |  |  |

# **List of Figures**

| Figure 2-1: | Digital Circuit Design Flow                               | 4  |

|-------------|-----------------------------------------------------------|----|

| Figure 2-2: | Butterfly Structure                                       | 10 |

| Figure 2-3: | BIST Structure                                            | 14 |

| Figure 3-1: | Fixed Rounder Algorithm                                   | 17 |

| Figure 3-2: | Configurable Rounder Structure                            | 18 |

| Figure 3-3: | Rounder Macro Hierarchy                                   | 20 |

| Figure 3-4: | Output Gain Stage Structure                               | 20 |

| Figure 3-5: | Butterfly Structures in Radix2 <sup>2</sup> SDF Algorithm | 23 |

| Figure 3-6: | Complex Multiplier Structure                              | 25 |

| Figure 3-7: | Top Level FFT Generation Flow                             | 28 |

| Figure 3-8: | FFT Stage Structures                                      | 29 |

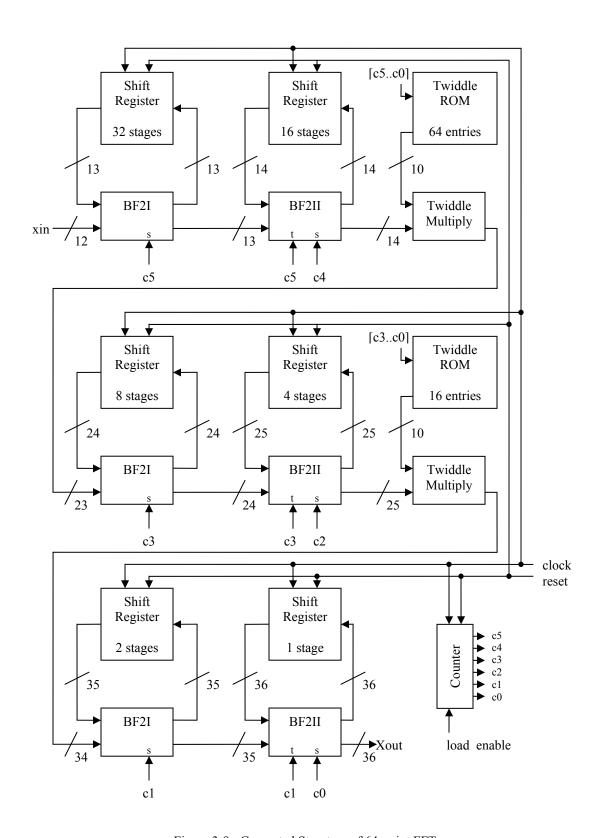

| Figure 3-9: | Generated Structure of 64-point FFT                       | 30 |

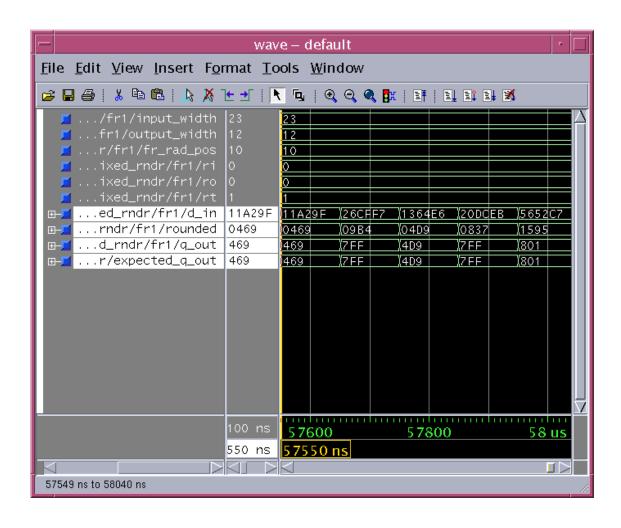

| Figure 4-1: | Sample of Fixed Rounder Test Bench Simulation             | 34 |

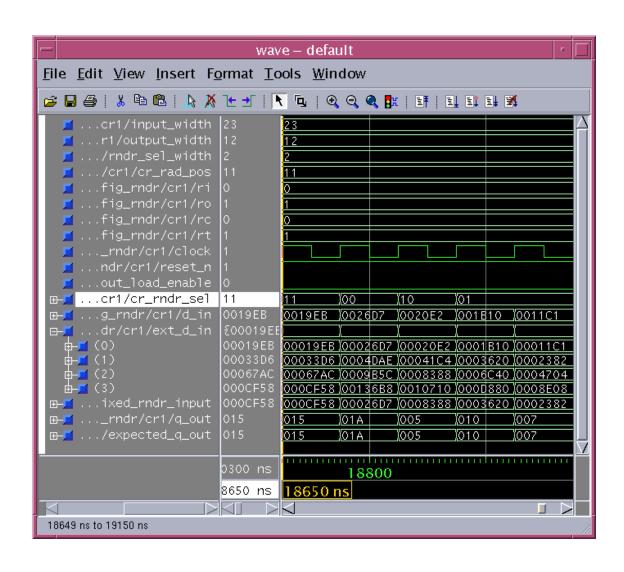

| Figure 4-2: | Sample of Configurable Rounder Test Bench Simulation      | 36 |

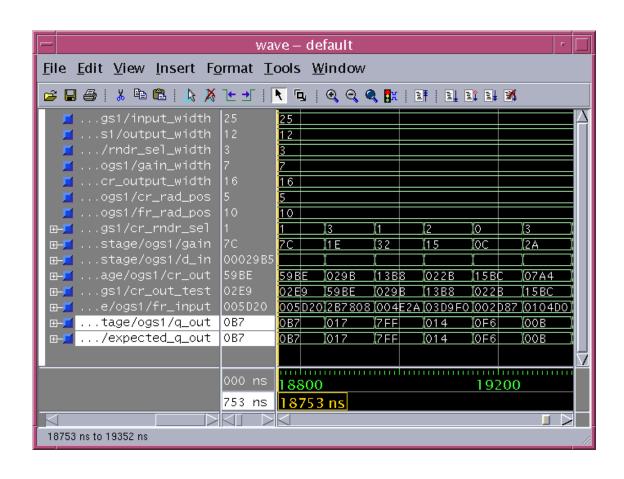

| Figure 4-3: | Sample of Output Gain Stage Test Bench Simulation         | 37 |

| Figure 4-4: | Pre-synthesis and Pre-layout Simulation Sample            | 39 |

| Figure 4-5: | Layout of the 64-point FFT                                | 41 |

| Figure 4-6: | Post-layout Simulation Sample                             | 42 |

| Figure 4-7: | Layout of Fabricated Chip                                 | 43 |

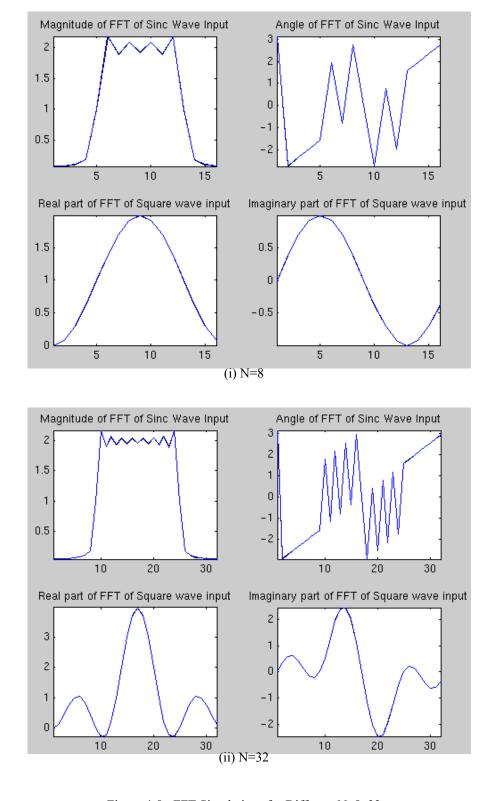

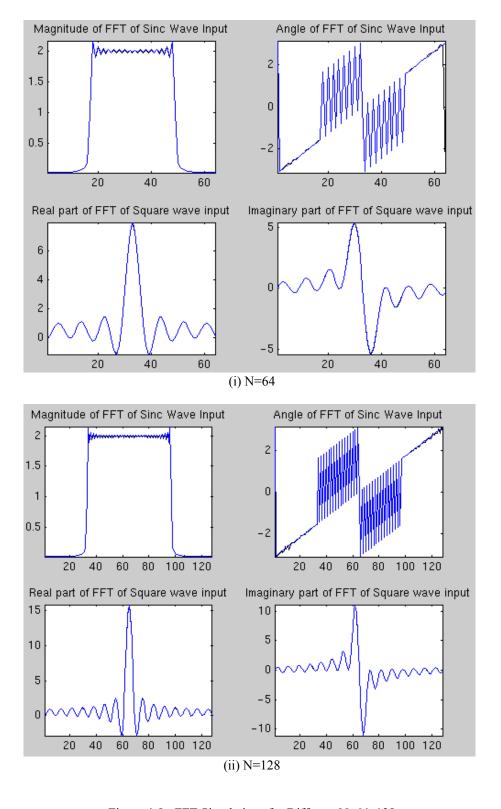

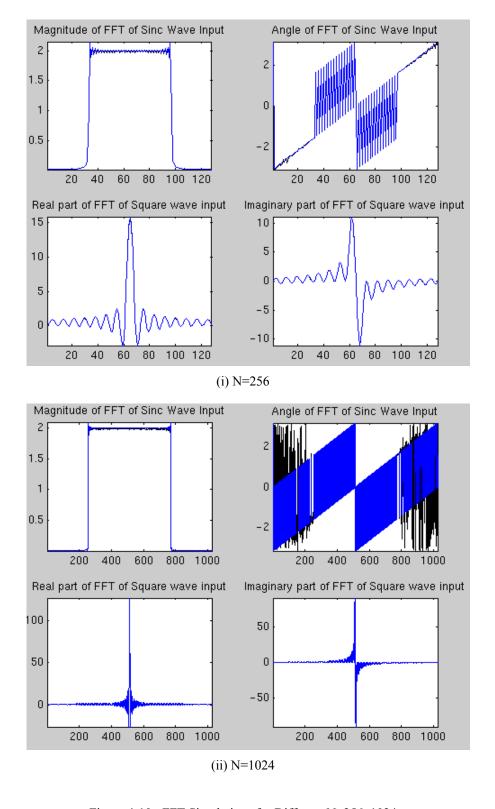

| Figure 4-8: | FFT Simulations for Different N: 8, 32                    | 45 |

| Figure 4-9: | FFT Simulations for Different N: 64, 128                  | 46 |

| Figure 4-10 | : FFT Simulations for Different N: 256, 1024              | 47 |

# **Chapter 1: Introduction**

Digital design is the process in which an algorithm is created in a digital system. As technology advances to create smaller and smaller transistors, the capabilities of digital systems grow. Digital systems are increasing in speed and capacity, and are decreasing in power. This opens up new markets for digital systems. For example, cellular phones with the ability to take pictures or record movies are a result of the digital systems in those components becoming more advanced.

As the capabilities of digital systems increase, more complex algorithms and designs can be created. This increasing complexity leads to a longer design time. Design time can be shortened to some extent by allocating more engineers or other resources to a project. This can be costly, however. If there is competition in a design's target market, longer design time can lead to loss of sales to a competitor. If a design is new or innovative, a shorter design time can lead to more sales before any competition enters the market. Thus, increasing design time is proportional to increasing costs.

One way to reduce costs is to build on existing designs. This can be hard to do, as the design might not have been initially created with the ability to build onto it in mind. Creating designs so the can be reused in later projects can solve this problem. By designing components to be reused, the design time decreases significantly. Making a design more flexible is one way to make it reusable. If the characteristics of an algorithm can be assigned specific parameters, it can be designed with the intent to make those parameters variable. Ideally, an entire library of parameterized macros would be created and added to.

Verification is important to the design process. Verification is a broad term describing all the testing that is done on a design. By testing at different points in the design process, errors are caught earlier and corrected. By catching errors earlier, costly mistakes can be avoided.

Digital signal processing is the study of real-world information that has been converted to a signal that a digital system can understand. Signals are gathered and then converted from an analog source to digital. This process is called sampling. By sampling signals fast enough, it is possible to represent them in a digital system with no loss of information. Signals that are sampled are in the time domain; they represent a point of data on a signal at a certain time.

One of the fundamental operations performed in digital signal processing is to convert a time domain signal to a frequency domain signal. A point in a frequency domain signal

represents the magnitude of a sine or cosine wave at that frequency. One type of algorithm that is used to convert between the domains, and is optimized for use in digital systems, is called the Fast Fourier Transform. This type of algorithm has many variations.

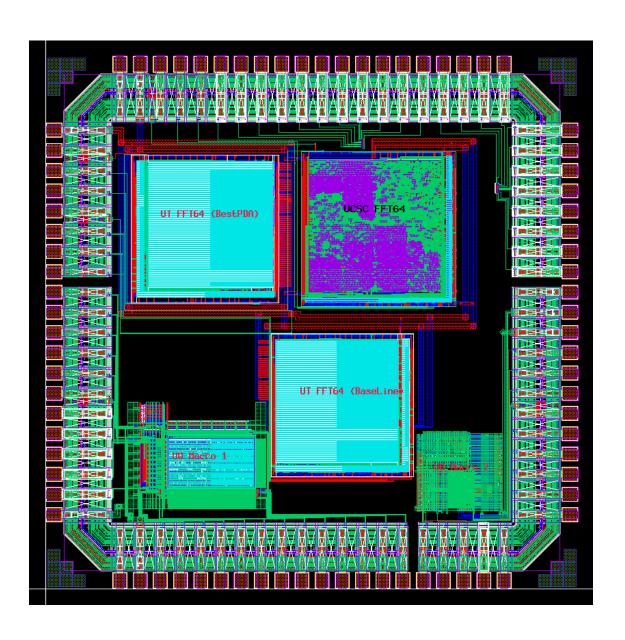

The work for this thesis was done as part of a research project with the Defense Advanced Research Projects Agency (DARPA) and Boeing. The research involved exploring ways to improve the power, delay, and area of application specific integrated circuits. Several macros were created to test, so all the groups involved would be able to compare their improvement methods based on the same code. Boeing provided the specifications for all the macros, and test benches for some of them, like the Rounder macros.

The goal of this research is to design and verify a parameterized Fast Fourier Transform macro as an example of the process used to create and test a parameterized design. The Fast Fourier Transform is used because the algorithm is moderately complex and it is used in a wide variety of digital signal processing applications. Several types of Rounders are also created as simple examples of a parameterized design.

By using the Fast Fourier Transform, this research will show that a complicated parameterized macro can be created and verified. It will show the range of flexibility that can be created. Verification will be performed in several stages of the design process. The design will also be fabricated and tested, completing the last step of verification. By creating the rounder macros, a simple parameterized macro is presented that is easier to understand than the Fast Fourier Transform macro.

# **Chapter 2: Background**

#### 2.1 VHDL and Design Flow

VHDL is a programming language that is used to describe hardware. It stands for VHSIC (Very High Speed Integrated Circuit) Hardware Description Language [1]. VHDL descriptions can be synthesized into field programmable gate arrays (FPGAs) and application specific integrated circuits (ASICs). FPGAs are commonly designed to be reprogrammable, so they are often used to test algorithms. ASICs are chips that are designed with a specific purpose in mind, and are generally not reprogrammable, but they are usually faster than FPGAs.

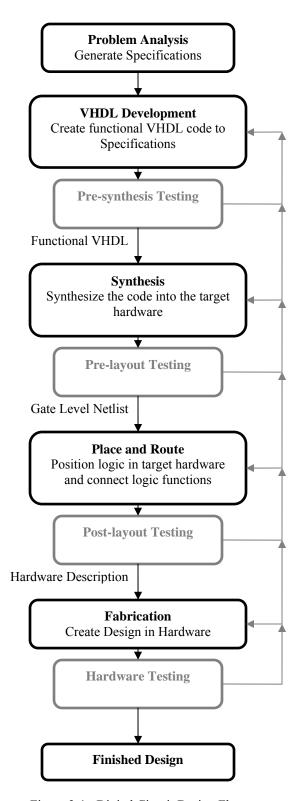

Figure 2-1 shows a basic flow for designing digital circuits. First, specifications for the design are created by analyzing the requirements of the problem. Then code is created to fit the specifications. In this example, the code is written in VHDL and tested to see if it is functionally correct. Once the code is functionally correct, it is synthesized. Synthesis is the process of translating the VHDL code into gates and logical functions of a specific technology. If the target technology is an FPGA, the hardware resources on the FPGA are allocated to the different logic functions of the code. However, the hardware resource assignments are not specific yet. For example, a hypothetical FPGA might have 2000 NAND gates available, and when a design is synthesized, it might require 50 NAND gates. The synthesis tool checks to see if 50 NAND gates are available, and if they are, it notes that 50 NAND gates have been used, but not which 50 were used. If the target technology is an ASIC, synthesis involves taking different logic functions from a library of standard cells. The standard cell library is created with cells that have different logic functions, and sometimes variants of the same logic function that are designed to handle higher loads on the outputs. The synthesis tool keeps track of which gates are used to synthesize different functions from the code. The design is tested again after it has been synthesized, and if it is correct, a listing of the logic functions and their connections, the gate-level netlist, is passed to the placement and routing step.

After the design has been synthesized, the hardware resources from the previous step need to be placed, and the connections between those resources routed. Placement and Routing, or PAR, involves attempting to increase the frequency the design can run at by decreasing the longest delay, or critical path. Some other goals during PAR can be decreasing the total hardware

Figure 2-1: Digital Circuit Design Flow

resources used, decreasing the power use, or some combination of the three. After PAR is finished generating the layout, and the layout is verified to be correct, the design can be realized in hardware. For FPGAs it is the process of configuring the FPGA with the design, which usually takes less than a minute. Fabricating an ASIC involves creating the design in silicon, and can take two months or more from the time the design is sent to the fabrication company till the chips are received by the designer.

The most important steps in the design flow are represented by the gray arrows and boxes in Figure 2-1. These highlight the testing and verification process. Between each step in the design process testing should be done to determine if the design is functioning correctly, based on the specifications. Testing can lead to changing the previous step or possibly going back several steps in the design process to correct an error that was not caught at earlier levels. The box labeled "Hardware Testing" represents the final tests done on the fabricated design to verify that it was fabricated correctly and there are no errors in the design. Only after the hardware is tested is the design process complete.

## 2.2 Design-for-Reuse

Design-for-reuse is a method of developing algorithms so they can be reused in other projects. This has the advantage of saving design time in later projects, but can cost more time in the initial development of the algorithm. By saving design time, it can reduce the number of engineers needed per project, speed up the time to market, and reduce expenses. One of the ways to design algorithms for reuse is to create code that is reconfigurable. The term "macro" is sometimes applied to a block of code if it is reconfigurable.

The more flexible the code becomes, the more likely that the code will be able to be reused. However, code that is highly flexible may be more complicated for a new user. This relationship leads to a balance between flexibility and ease of use. One way to keep the code easy to use is to provide default settings for some of the things that can be reconfigured. A user that is more familiar with the algorithm can then go in and modify these default settings for an application that requires it.

In VHDL, there are two primary ways to create reconfigurable code. The first is using the **generic** declaration [2]. **Generics** can be described as constants that can change with different instantiations of the same block of code. In other words, **generics** are a way of specifying parameters for a given instance of a block of code. For example, a counter could be

created using a **generic** that stopped at a certain value. Each time the counter block is used, a different stop value can be passed to the block. Another example is a shift register with variable numbers of stages. The number of stages could be passed to the block of code, so the same block of code could be used any time a shift register is required. To make it even more flexible, the width of the data being sent into the shift register could also be assigned as a **generic**. The following code is the declaration of a shift register using **generics**. It is designed to perform a

```

entity shiftregN is

generic( data_width : integer :=25;

n : integer :=4);

port( clock, resetn : in std_logic;

write_data : in std_logic_vector(data_width-1 downto 0);

read_data : out std_logic_vector(data_width-1 downto 0));

```

shift whenever the clock is rising and the resetn is high. Note that the width of read\_data and write\_data is specified by the generic data\_width. Because data\_width and n are assigned default values, it is possible to skip mapping **generics** to the block when it is instantiated in a higher-level function, and just use the default values.

The second way to create reconfigurable code is to use the **generate** statement. The **generate** statement is handled during synthesis, and can simplify the logic needed for an algorithm. There are two types of **generates** that can be used to create flexible code. The first is called a "conditional **generate**". This type of statement will allow logic to be created during synthesis if a certain condition exists. For example, the following code is designed to

```

assign_a: if a_in=1 generate

Y<=A;

end generate assign_a;

assign_b: if a_in/=1 generate

Y<=B;

end generate assign_b;</pre>

```

assign an input signal, A, to the output signal Y if a\_in is equal to 1. A second conditional **generate** is included to assign B to Y if a\_in is not equal to 1.

There are many circumstances where conditional **generates** can be used. For example, an algorithm might call for the ability to add or remove pipeline registers before synthesis, to test timing. Conditional **generates** could be applied to this requirement so that the only difference in the code between the pipelined and unpipelined version is one **generic** assignment. The main advantage to using conditional **generates** is that they allow for different hardware options when designing an algorithm. Unused options will not be synthesized, lowering the amount of resources required compared to a version that includes redundant logic.

The second type of **generate** statement involves a loop. This type of **generate** is useful when an operation needs to be repeated, either in parallel or in series. Examples of this include adder trees and multipliers. Loop **generates** can also be used within conditional **generates**, and the reverse works as well. By combining them with **generics**, it is possible to create code that is flexible, and is more likely to be reused in future designs. More examples of code with **generic** and **generate** statements can be found in *The Designer's Guide to VHDL*,  $2^{nd}$  *Edition* [2], or online at "The VHDL Language Guide" [3].

#### 2.3 DSP

In this section, an overview of Digital Signal Processing, or DSP, will be given, and background information on two different aspects of DSP will be presented. The first is the Fast Fourier Transform, and how it works in general. Information about the specific algorithm developed will be presented in the Implementation chapter. The second aspect that will be presented is rounding. This aspect is presented because the theory behind it is easy to understand, and it makes a good example of a simple parameterized algorithm.

#### 2.3.1 Overview

Digital Signal Processing is used in a wide variety of applications. Some examples include voice recognition software, automatic target recognition for weapons, and cellular phones. Any time a signal from the real world is analyzed as a digital representation of that signal, some form of DSP is being applied. DSP can be performed in the time domain, taking the values of the signal and manipulating them, or the signal can be converted to the frequency domain, and processing can be done there. Both have different advantages, and converting between them is usually done with a Fast Fourier Transform.

Digital signal processing has its roots in analog signal processing, but instead of using numbers to represent signal values, the actual signals are used in analog signal processing. The

equations and filtering techniques of DSP are circuits made from resistors, capacitors, inductors, and operational amplifiers. For example, band pass filters can be created using operational amplifiers and some resistor and capacitor networks. In analog signal processing, this filter has a certain range of signal frequencies that it will allow to pass through with little to no change, and as the signal frequencies get farther away from the passed band, they are decreased. A DSP version of the same filter is ideal. It is possible to control the pass band, and remove any signals not in the pass band, instead of decreasing them gradually. However, there are two fundamental problems with digital signal processing: quantization and sampling.

Both quantization and sampling problems are introduced when the analog signals being processed are converted to digital. This conversion is referred to as analog to digital conversion, or ADC. Typically, ADC is done on voltage levels, but it can be applied to other analog signals. During the conversion process, the strength of the input signal is compared to the maximum input value, and assigned a number. For example, if you had an ADC that took an input signal from 0 to 5 volts, with an output range of 0-255, and a 3.20-volt signal were the input, the output would be 163.84. However, the output is limited to whole numbers, so it would either be 163 or 164. The potential for two different results is the quantization error. A way to minimize this error is to increase the output range of the ADC, which is equivalent to increasing the bit-width of that digital signal. Using the same example with a 12-bit ADC (output range of 0-4095) gives a result of 2621.44. There is still an error, but the error is smaller by a factor of 16, because the 12-bit ADC can detect much smaller quantum differences in the signal than the 8-bit ADC.

Sampling problems are related to how fast the ADC can run. How often the ADC outputs the converted signal value is called the sampling frequency. Because the signal is not continuous anymore, there is a limit on the maximum frequency that can be represented by the digital signal. To accurately represent the signal, there cannot be any data in the signal that is at a frequency higher than half the sampling frequency. This limit is called the Nyquist frequency [4]. Sampling at higher frequencies can solve this problem.

Once a signal is converted from analog to digital, there are two different domains to process the signal. The first is the time domain. Signals in this domain have different magnitudes at different times. This is how we perceive all signals. All DSP begins with signals in this domain, and they can be converted to the frequency domain and back again. In the frequency domain, signals are represented as different magnitudes at different frequencies [5].

There are advantages and disadvantages to processing in each domain. One of the advantages of time domain processing is the ability to further sample the signal. Windowing, or allowing the signal to pass for a certain amount of time, is also easy to accomplish in the time domain. However, it is limited in its applications. Many types of filters are easier to realize in the frequency domain. Simple low pass filters are much less complicated in the frequency domain than the time domain. Correlation is also much easier to determine in the frequency domain. The key disadvantage of the frequency domain is that it deals with blocks of samples instead of a continuous stream of samples.

# 2.3.2 The Fast Fourier Transform

The Fourier analysis, named after Jean Baptiste Joseph Fourier, is a process in which a signal is broken down to sinusoidal waves, with varying frequencies and amplitudes. This is done to make it easier to perform mathematical operations on the signal. There are two different traits of the signal that set how the signal will be processed. If a signal is periodic, meaning it will repeat to infinity, and continuous, then the type of Fourier transform that is performed on it is called the Fourier series. If the signal is not periodic, but still continuous, then the transform is called the Fourier Transform. Sampled signals that are not periodic are transformed using the Discrete Time Fourier Transform. Finally, signals that are sampled and periodic are processed using the Discrete Fourier Transform or DFT [4].

The DFT can be expressed as a simple equation. In this equation, k runs from 0 to N/2. This form of the DFT only shows the positive half of the frequency range, but it is commonly

$$X[k] = \sum_{i=0}^{N-1} x[i] \cos(2\pi ki/N) - \sum_{i=0}^{N-1} x[i] \sin(2\pi ki/N)$$

(1)

represented as the range from -N/2 to N/2. N is the number of samples being taken. Directly implementing this formula would result in an execution time that is proportional to the number of samples squared.

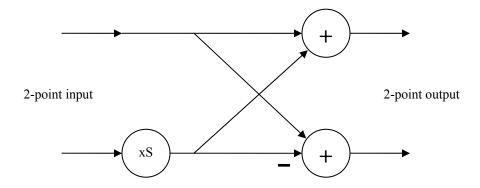

The Fast Fourier Transform, or FFT, is an algorithm that simplifies the DFT. By processing x in a different order and breaking the operation down into the structure shown in Figure 2-2, it is possible to calculate the FFT with an execution time that is proportional to  $N\log_2(N)$ . The structure shown in Figure 2-2 is called a butterfly, and it is the basic building block of most FFT algorithms.

Figure 2-2: Butterfly Structure

Because of the way the FFT is structured, it can be used to convert from a frequency domain signal to a time domain signal. This is called the Inverse Fast Fourier Transform, or IFFT. To convert it, the frequency domain signal is run through the FFT algorithm. Then, the samples from n=1 to n=N-1 are mirrored around (N-1)/2 [6]. The sample at n=0 is unchanged. By reversing most of the signal, it has converted from an FFT to an IFFT.

#### 2.3.3 Rounding

Rounding is also important to DSP. Some operations produce outputs that are significantly larger than one of the inputs. Multipliers, for example, produce an output with a bit width equal to the sum of the input bit widths. Connecting several of these types of operations together can lead to very wide signals. This can lead to the use of large amounts of hardware resources. One way to compensate for this is to truncate the signals to a smaller size. However, this reduces the accuracy of the data. A balance between the two is to round the data off instead of truncating it. Rounding in binary is much simpler than rounding in decimal. In binary, if the signal is positive and the bit to the right of the rounding point is one, then it rounds up. What makes this simpler in binary is the check to see if the digit above the rounding threshold is removed. By adding the bit to the right of the rounding point to the bits to the left of the rounding point, a positive number will be rounded.

Sometimes a certain level of accuracy is required, and some lower bits of data cannot be lost. In this case, rounding is not an option. Instead, the higher level bits are cut off. A contingency is put in so that if the signal is too large for the remaining bits to represent, it will set

the signal to the maximum value it can represent. Combining this with a rounder leads to a very flexible block of code that can be used for either rounding or truncating depending on the situation.

#### 2.4 Verification

In this section, verification and testing will be discussed. After presenting an overview of verification, different simulation types will be discussed. Finally, testing will be discussed, with the focus on having test circuitry as part of a fabricated design versus having separate test circuitry.

#### 2.4.1 Overview

Verification is an important part of system design. It is the process of verifying the functionality of the system at different stages of the design process, usually by providing some functional input to the design and comparing the output to the expected output. Testing and verification can reduce costs in designs by reducing the chance that some or all of the design will not work when fabricated. By testing at many different levels of the design process, it is easier to isolate where problems are introduced and correct them. Verification should place the design under stress, so that it can be shown to be working for most of the combinations of parameters. By testing to the limits of the specifications, it is more likely that problems throughout the range of the specifications will be caught.

There are two different ways to verify that a design is working as intended. The first is to create a model of the system in a higher-level language that will produce bit-true results. This has the advantage of matching the output from the design exactly. It may also be possible to create the model so that internal values are bit true also. This is very helpful in debugging the design. However, developing a bit-true model can take a long time, depending on the algorithm and how it was originally created.

The second method of verification is to create an approximate model, or use an existing model that will produce similar results. This has the advantage of being easy to develop, and can require less time to develop, because it is not an exact model. In the case of DSP, there are existing tools that can duplicate some algorithms very easily and quickly. The disadvantage is that the output from the design must be compared to the output from the model, and they might not exactly match. It must then be determined, by looking at the outputs and the algorithm, if the design is working as intended.

#### 2.4.2 Simulation Types

When performing tests on the design, there are two different options that are available at most stages of the design process. The first is an event driven type of simulation. In this type of simulation each operation is assumed to take a certain quantum delay,  $\Delta$ . For example, if a process assigned a value to a signal on the rising edge of the clock, and the clock edge occurred at 100ns, then the output would change at 100ns plus  $1\Delta$ . This type of simulation can be fast, but it is not accurate for timing, only for logic. The second type of simulation is much more complicated. It can only be performed after the system has been synthesized. It uses models of the gates involved and SPICE, a circuit simulation tool, to calculate what the voltages are for every net in the system. This type of simulation can be more accurate, but because of the number of calculations involved, it usually takes more time to perform. A SPICE simulation can take ten times longer or more to perform.

Simulation should be performed at each stage of the design process. Doing so makes it easier to go back to a higher level of abstraction to correct an error. As the design becomes less abstract, the simulation must become more accurate. A purely event driven simulation would not be useful after the layout is generated, because it would not take into account the layout itself. Also, an approximation type of simulation should not be used past the Pre-synthesis testing stage. The results of the Pre-synthesis testing can be used to compare with the test results of the later stages.

At the Pre-synthesis stage, an event driven simulation can be useful to determine if the algorithm has any errors. If the test vectors and expected output are approximate instead of bit-true, the outputs from the design at this stage should be used in later simulations to confirm that they are accurate. It should be noted, however, that because there is no timing information at this stage in the design process, intermediate values can be inaccurate when compared to values in later stages. The stable results should be correct, however.

After the design has been synthesized, it is known what logic blocks will be used to create the algorithm. In ASICs, these logic blocks can be standard cells. In FPGAs, these blocks are usually specific to the hardware being targeted. At this level, an event driven simulation with timing information can be performed. This is similar to the previous stage, but instead of assuming a  $\Delta$  delay for each operation, the delay of each gate is known according to the load on the gate. This timing information can be calculated based on the SPICE model of each gate and the load characteristics it will be under. This produces a more accurate test. Testing is done at

this level because it is possible to introduce timing errors when the delay for the gates has been introduced into the system. For example, in a system where some combinational logic is between two registers, there might be too many gates between the registers, causing an error to occur. This level of simulation does not take into account the wire delays, because while the type of hardware is known, the position of the gates relative to each other is unknown. This will introduce more delay, and is included in the next step. It is also possible at this step to perform simulations using a fixed timing value for each gate. By not calculating the delays of each gate, time is saved at the cost of accuracy of the simulation. If the timing for the gates is estimated to be higher than the actual delay and there are no problems with the simulation, it is likely that the system is still working correctly.

Simulation after the layout has been generated is the most important simulation to perform. At this stage, the logic required and its locations are known. This means that the length of the wires and the delay that they introduce to the system is also known. As technologies decrease in feature size, wire delay is becoming more of a problem. At this level, it is still possible to calculate the delay of the gates and the wires connecting them, making the event driven simulation with delay information a good way to simulate the system. SPICE simulation is possible, but it can take a long time to generate the net list, and takes a long time to run through each simulation. If the delays are calculated, which is called back annotation, the input stimulus can be changed easily and the simulation can be run faster than a SPICE simulation. While SPICE will give the most accurate results, performing an event driven simulation with timing information will give a good estimate for significantly less time involved.

#### 2.4.3 Testing

After creating a design in hardware, either through fabricating an ASIC or programming an FPGA, it is necessary to test the design to verify that it is working. Ideally, the behavior of the post-layout simulation is very close to what the hardware will be, so any design problems the hardware would have had are already solved. Testing can either be done with hardware in the chip, or by test equipment outside the chip.

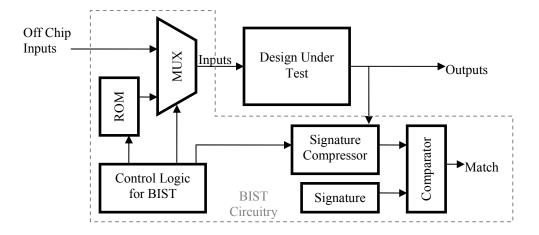

One way to put test equipment on the chip is with a built in self-test, or BIST. Figure 2-3 shows an example of a BIST. In order to use the BIST, a set of test vectors are chosen and programmed into the ROM. After the test vectors are chosen, they are used with the design under test and the signature compressor to generate a signature. The signature is the output of the signature compressor after all the test vectors have been input. An alternative to using a ROM

Figure 2-3: BIST Structure

and test vectors is to use a counter or other type of number generator. Signature compression is an algorithm that retains a memory of the previous compressor outputs and performs some XOR operations on the previous output and the next input to the signature compressor. Since it has feedback, it is only done on the rising edge of the clock. Additional XOR gates are inserted between different outputs, so with no input it will output a continuous stream of numbers and will not repeat any until it has cycled through all the possible outputs. This type of signature compressor is called a Linear Feedback Shift Register or LFSR [7].

After the signature has been generated in simulation, it is programmed into the VHDL for the BIST. When the BIST is run, it feeds the test vectors into the design under test and compresses the output in the signature compressor. After the test vectors are finished running, it compares the output of the signature compressor to the simulated signature. If they match, the comparator outputs a signal that acknowledges they match.

There are several advantages to having the testing circuitry as part of the design. One advantage is that it allows the test mode to be simple, with minimal external hardware required. This advantage is important in a research or teaching environment, where testing equipment for specific hardware may be too expensive. The second advantage is that the testing hardware runs at full speed. Instead of having delay going on and off the chip and delay caused by any circuitry from external test equipment, there is very little delay between the testing circuitry and the design under test.

There are drawbacks to this approach also. While there is very little delay between the test circuitry and the design under test, the test circuitry adds some delay to the overall design. This slows down the overall performance of the chip. The second disadvantage is in having extra circuitry on the chip. Having the extra circuitry on the chip takes up more space and the power consumption increases.

If space, power, and speed cannot be sacrificed, another way to test a design is to put the test circuitry off the chip. In addition to decreasing the space and power required for the design, it allows the user to create new test vectors and input them into the circuit. Depending on the complexity of the testing hardware, the test board can be expensive. Running extra test circuitry can slow down the design, because of the time required to get the test vectors onto the chip and the outputs off of the chip.

# **Chapter 3: Implementation**

#### 3.1 Rounders

There are three different rounder blocks that have been developed for this paper. They are being presented as an example of parameterized code. The lowest level is called the Fixed Rounder. Additional hardware is added to the Fixed Rounder to create the Configurable Rounder. The third rounder also performs some shifting on the data and is called the Output Gain Stage. Code for the Rounders is included in Appendix A.

#### 3.1.1 Fixed Rounder

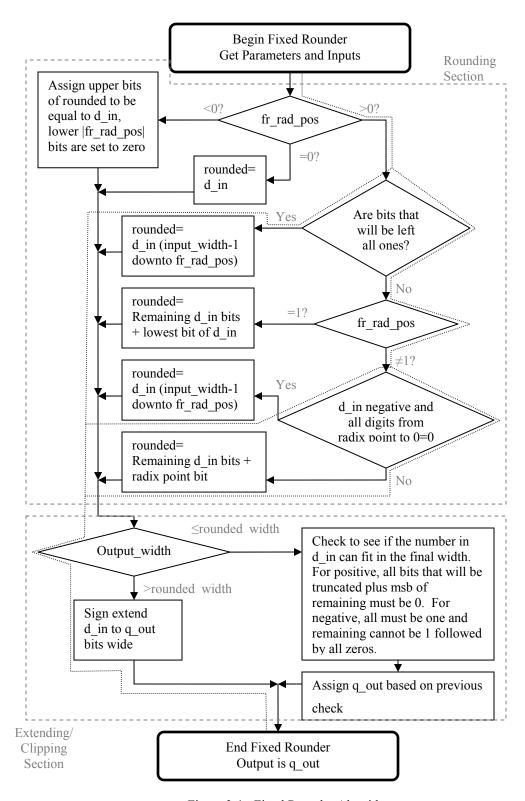

The Fixed Rounder block is designed to take an input (d\_in) of input\_width bits wide. It then is rounded at the radix position set by the fr\_rad\_pos parameter. After rounding, the output is set to be the lowest output\_width bits in the rounded number. If the number is too large to be displayed in output\_width bits, the rounder will set the value to the maximum. Normally negative number can reach a value of (output\_width-1)², but the Fixed Rounder will limit the output magnitude to (output\_width-1)²-1. Figure 3-1 shows the logic for the Fixed Rounder. The output of the Fixed Rounder is q\_out.

In addition to the flow shown in Figure 3-1, other parameters are used to specify whether or not there is a pipeline register on the input (ri), what kind of register is on the output (ro), and what type of reset the registers use (rt). When ri is zero, there is no register on the input and when it is one, there is a pipeline register on the input. The pipeline register inserts a delay of one clock cycle, and how it is reset is controlled by rt. If rt is 0, there is no reset. When rt is 2, the reset is asynchronous. The default value for rt is 1, and has a synchronous reset then. For the output register, ro has the same behavior as ri if ro is zero or one. It can also be set to two, which will insert a register that only outputs on the rising edge of the clock and when the out\_load\_enable signal is set to high. This type of register is referred to as a "z register." If ri and ro are zero, then the clock, reset\_n, and out\_load\_enable signals are not needed.

Once the fixed rounder is synthesized, all the parameter values are fixed. For example, if a Fixed Rounder block had fr\_rad\_pos equal to 4, input\_width equal to 12, and output\_width set to 10, it would take the path shown by the dotted line in Figure 3-1. The

Figure 3-1: Fixed Rounder Algorithm

line can take several different routes, depending on what the value of d\_in is. Logic not on the path shown will not be synthesized, because it is redundant. This means that each time the Fixed Rounder is instantiated, it will only round a specific bit width at a specific radix point, and will only extend or truncate to a fixed output width.

#### 3.1.2 Configurable Rounder

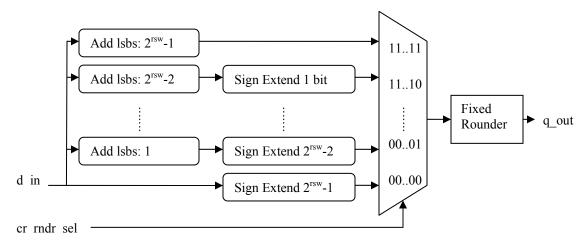

The Configurable Rounder expands on the Fixed Rounder. By creating an array of input signals to be selected, it allows for the radix point to be adjusted dynamically. Figure 3-2 shows how the array is created and how it interfaces with the Fixed Rounder block. In the figure, rsw is the rounder select width (rndr\_sel\_width in the code), which is the bit width of the cr\_rndr\_sel input. The width of the data input, d\_in, is controlled by the parameter input\_width. The width of q\_out is controlled by output\_width. When the Fixed Rounder block is instantiated, it uses an input width of input\_width plus 2<sup>rsw</sup>-1, and an output width of output\_width. The radix position for the Fixed Rounder is controlled by fr rad pos in the Configurable Rounder.

The main purpose of the Configurable Rounder is to take signals and round them at different radix points. This is accomplished by using the sign extension operations and padding least significant bits (lsbs) with zeros to shift the desired radix point to the radix point to which the fixed rounder is set. For example, if the fixed rounder was set to round on the fourth bit, and d\_in needs to be rounded on the third bit, it can be padded by one zero on the lsb, and sign extended so the width will be the width of the fixed rounder input. The third bit has been shifted

Figure 3-2: Configurable Rounder Structure

to the fourth bit position, so the fixed rounder will round on the correct bit. Another use for the configurable rounder is to shift signals down to the same magnitude. If a series of inputs is known to have different radix points, and the numbers are going to be added together, then they need to be shifted so they all have the same radix point before they are added together. By using the Configurable Rounder, it is possible to select the correct amount of shifting to move the radix point to the desired location. Rounding can be done on the information to decrease the size of the operations that will follow the Configurable Rounder. This algorithm can have problems with making some parameters too large. As the rsw parameter increases, the number of inputs to the multiplexer grows proportional to the square of rsw.

As with the Fixed Rounder, the Configurable Rounder also has ri, ro, and rt as parameters. In addition to parameters setting the input and output register types and reset type, there is a parameter to set a register on the cr\_rndr\_sel input. This parameter is called rc, and it has values associated with it similar to ri (0 is no register, 1 is a pipeline register). The ri parameter on the Fixed Rounder is set to 0, and the ro parameter is mapped to the ro parameter of the Configurable Rounder. It should be noted that there are no generate statements in the Configurable Rounder that are based on ro, the Fixed Rounder handles ro exclusively.

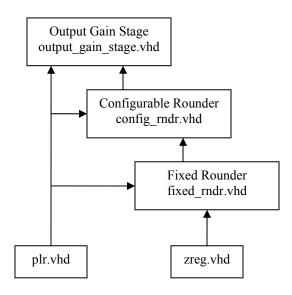

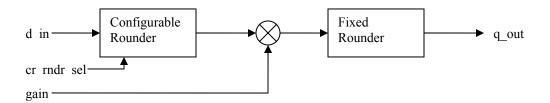

## 3.1.3 Output Gain Stage

This block is the final type of rounder block. It is the highest block in the rounder hierarchy, as show in Figure 3-3. Also shown are two other blocks of code, plr.vhd and zreg.vhd. These blocks are the pipeline register and z register, and have their input width and reset type parameterized. This allows them to be used in a variety of situations.

The Output Gain Stage is designed to take an input vector (d\_in), run it through a Configurable Rounder to make the vector smaller, and then multiply it by another input, gain. The output of the multiplier is sent into a Fixed Rounder block so the next block in the DSP algorithm can be loaded with the right number of bits. Figure 3-4 shows the overall layout of the Output Gain Stage. The goal of the Output Gain Stage is to scale an input signal to a range and overall width that will produce useful results in the next processing stage. The Configurable Rounder in this design rounds d\_in to a smaller value, which makes the multiplier smaller. When the output from the configurable rounder is multiplied by gain, the answer has a width equal to the gain width plus the croutput width of the Configurable Rounder.

Figure 3-3: Rounder Macro Hierarchy

Figure 3-4: Output Gain Stage Structure

By setting the ri parameter to one in the instantiation of the Output Gain Stage, a pipeline register is inserted on the input. The input register is handled by the Configurable Rounder block. In the Configurable Rounder block, ro is set to zero, which means there is no output register in that block. The rc parameter of the Configurable Rounder is inherited from the Output Gain Stage. If rc is set to one in the Output Gain Stage, a pipeline register is inserted to delay the value of gain. Because the Configurable Rounder inherits rc, if there is a register on gain, there will be a register on the cr\_rndr\_sel input. Additionally, the cr\_rad\_pos, rndr\_sel\_width, and output width are all set when the Output Gain Stage is instantiated.

An additional register is inserted into the data flow if the parameter pr is one. This register is for pipelining the algorithm. When the register is enabled, it is inserted between the Configurable Rounder and the multiplier. No register is inserted between the gain and multiplier. Because of the mismatch in delays, designs using the Output Gain Stage need to take the difference in levels of delay. Another solution to this problem is to not include an extra register on the output for simulation before synthesis, and use a synthesis tool that can allocate pipeline registers into a design automatically.

As in the Configurable Rounder, the Fixed Rounder handles the ro parameter of the Output Gain Stage. The ri parameter of the Fixed Rounder is set to zero, the input width is set to the output width of the multiplier, and the output width is set to the output width of the Output Gain Stage. The radix position is set when the Output Gain Stage is instantiated.

#### 3.2 FFT

The FFT macro that has been created is using an algorithm called the Radix- $2^2$  Single Path Delay Feedback (R2<sup>2</sup>SDF) algorithm [8]. This algorithm takes a natural order stream of complex number inputs, one per clock cycle, and outputs a stream of complex numbers in bitreversed order. Bit-reversed order means that if a counter counted each point of data that was coming out, and reversed the order of the bits in the counter, that would be the sample number corresponding to that point of data. For an N point FFT, there are N-1 registers used in feedback shift registers,  $2 \log_2(N)$  complex adders, and  $(\log_2(N) - 1)/2$  complex multipliers, with any fractions dropped. Log<sub>2</sub>(N) is the number of butterfly stages that will be in the design, and are numbered from one to  $\log_2(N)$ . First the components will be described from the lowest level up to the higher levels, then information about the test bench and how the test vectors are created

will be presented. Code for the FFT is in Appendix B. There are also some commercially available FFT cores. For example, Xilinx has one available in their IP Center [9].

#### 3.2.1 Shift Registers, Adders, and Subtract Modules

Shift registers are used in this algorithm to provide feedback. Two different modules have been created to fill this role. The first is shiftreg1, which is a 1-stage shift register with the input width set by data\_width. The second is shiftregN, which is an N-stage shift register with input width set by data\_width as well. In the first stage of the FFT, the shift register is set to N/2 stages. Each FFT stage after divides the number of shift register stages by 2, until shiftreg1 is used in the last FFT stage.

Adder and subtract macros are included to reduce the amount of recoding necessary to replace add and subtract operations. It is possible to map operators to macros to different operations. For example, it is possible to map the "+" operator to a macro that adds the two numbers together and returns the sum. If the "+" operator is not mapped to a macro, the adder macro used could be replaced with an adder of a different design. The same applies to normal multiplication and subtraction.

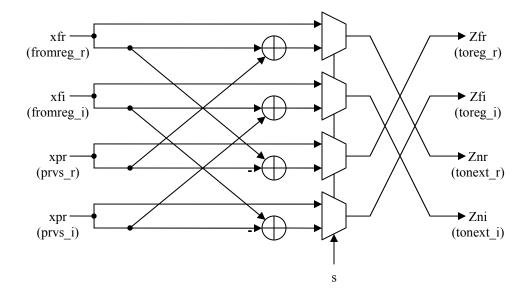

#### 3.2.2 Butterfly Types

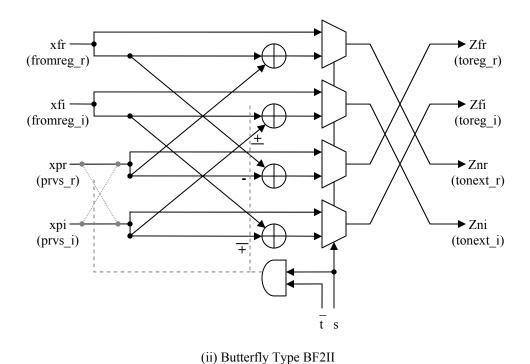

There are two different butterfly structures used in this FFT algorithm. The two types of butterflies are shown in Figure 3-5. The names in parenthesis are the names of the signals in the code. The last letter is to signify if it is the imaginary component of a signal or the real component of a signal. As an example, xfr and xfi are the imaginary and real parts of the complex signal xf.

Both butterflies share a control signal s, which controls four multiplexers. The signal s is driven by a bit in the control counter. The counter has a range of zero to N-1. Each stage is driven by a different bit, with the first stage driven by the  $\log_2(N)$  bit of the counter, and the last stage by the lowest bit of the counter. This signal switches the butterfly between two different modes. When s is zero, the butterfly is in passing mode. When in passing mode, xf and xp are passed to Zn and Zf, respectively. When s is one, the butterfly is in butterfly mode. In this mode, the butterfly operation is performed and the answers sent to the output signals. The BF2I butterfly is used for the odd numbered stages, including the first stage, and the BF2II butterfly is used in the even numbered stages.

(i) Butterfly Type BF2I

Figure 3-5: Butterfly Structures in Radix2<sup>2</sup>SDF Algorithm

The control signal t is used in BF2II to add some extra functionality to the butterfly. When t is zero and s is one, the data in the butterfly is routed differently, and some of the addition and subtraction operations are performed differently. First, the real and imaginary parts of xp are switched. This causes the first and third operations to change from xfr + xpr to xfr + xpi and xfr - xpr to xfr - xpi. The second and fourth operations also change. The second changes from xfi + xpi to xfi - xpr, and the fourth changes from xfi - xpi to xfi + xpr. The code for this is implemented slightly differently. The components of xp are still switched, but instead of changing the type of the second and fourth operation, the outputs are switched. This data manipulation in the BF2II stage is for one purpose. The entire operation mimics multiplying the xp input by -j. Performing the operation this way saves space, because a complex multiplier is unnecessary. This multiplication is needed for the algorithm to function correctly, and is done to simplify some of the twiddle factor multiplication. The control signal t is equal to the s bit of the previous stage.

Both butterflies have two parameters, the output\_width and add\_g parameters. The add\_g parameter is the adder growth, and can be either zero or one. Whenever binary numbers are added, the output width grows to be one bit bigger than the input width. The add\_g parameter regulates if the extra bit is added onto the signal, or if the signal will remain the same size. For example, if the output width is 12 and add\_g is set to one, the input width will be 11. The signal xp is the only input signal set by input\_width, all the rest are set by output\_width. The signal xf is set by output width because it is input from the feedback shift register. The shift register has Zf as the input, so the width of xf and Zf must match.

Suppose an instantiation of BF2I has an output\_width of 13 and an add\_g of 1. In order for the adders to function properly in this version, they must have the same width input and output. The signal xp must be sign extended to match the width of xf. The sum of the different components will then be 14 bits. A special multiplexer, mux2mmw, is inserted to handle the signals with mismatched width. The output from this multiplexer is 13 bits wide.

The highest bit in the adder can be truncated because of how the butterfly and shift register work together. The butterfly in each stage is controlled by a bit in a counter. The controlling counter will be discussed more in a later section. Because it is a counter, the s signal will only be high for a number of clock cycles equal to the depth of the shift register for that stage. For example, the first stage in a 64-point FFT has a shift register that is 32 stages deep.

For the first 32 clock cycles, the butterfly is in passing mode, and is filling up the shift register with the 12-bit inputs. For the next 32 clock cycles, the butterfly is active, and the shift register will be filling inputting the 13-bit results of the butterfly operations, and will be outputting the stored 12-bit values. For the next 32 clock cycles, s is low again, so the shift register will be outputting the stored 13-bit values, and storing new 12-bit values. The process then repeats itself. Never is a 13-bit number added to a 12-bit number, only 12-but numbers are added to 12 bit numbers. The same is true of the BF2II stage.

#### 3.2.3 Complex Multiplier

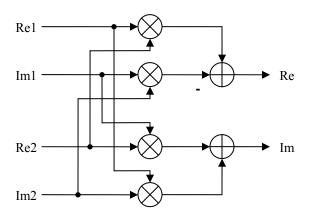

At each even-numbered stage, except the last if it is even, the Zn complex signal from the BF2II butterfly is multiplied by a complex twiddle factor. Figure 3-6 shows the structure of the complex multiplier. The input width of the two inputs can be different. The addition and subtraction operations are performed on signals of the same width, since every input to those operations comes from the product of one part from each signal. This means that real and imaginary parts of each signal must be the same width.

The multiplier growth parameter (mult\_g) is used to limit the output of the multiplier. In this design, each instantiation of the complex multiplier is multiplying by the same width signal for the second input, called twiddle factor width. The first input is the output from the BF2II stage, and the second is the twiddle factor, from the ROM storing the twiddle factors. The output from the multiplier is equal to the output width of the BF2II output plus the parameter for

Figure 3-6: Complex Multiplier Structure

the twiddle factor width, twiddle\_width, plus one. The additional one comes from growth during the addition and subtraction operations. In the complex multiplier, add\_g is part of mult\_g. The output from the complex multiplier is truncated to be equal to the first input's width plus the mult\_g parameter. This limits the mult\_g parameter to a range from zero to the twiddle\_width plus one.

#### 3.2.4 Twiddle Factors

In the R2<sup>2</sup>SDF algorithm, every even stage has a complex multiply by a complex twiddle factor. In this version of the algorithm, the twiddle factors are generated ahead of time in MATLAB and written to a VHDL file that contains a case structure. The case structure it generates is similar to a ROM, and a ROM could be substituted for it easily. It will be referred to as the twiddle factor ROM or just ROM. The MATLAB code to generate the ROMs is in Appendix C, as is all the other MATLAB code.

The following equation is used to generate the twiddle factors. In this equation, N is the

$$W_i(x) = e^{(-2j\pi x(k/N))}$$

(2)

total number of points in the FFT, and x ranges from zero to the number of points in the ROM divided by 4. The number of points in the ROM, m is equal to the number of shift registers in this stage multiplied by four. The variable k changes as a function of the number of points. For the first m/4 points, k is equal to 2\*N/m. For the second m/4 points, k is equal to N/m. For the third, k is equal to 3\*N/m. For the last m/4 points, k is equal to zero. The result of taking the  $e^0$  is one for the real part and zero for the imaginary part, so the last m/4 points are one for the real parts and zero for the imaginary.

The width of the twiddle factor is controlled by the twiddle\_width parameter. When MATLAB generates the twiddle factors, it is initially not in a fixed-point format. To scale them, they are multiplied by  $2^{twiddle_width}-1$ . Any fractions are dropped, and then they are converted to two's compliment form. This is done separately on the real and imaginary parts of the twiddle factors.

To make the process of generating the ROMs easier, a different MATLAB program is designed to repeatedly call the ROM generator program. It generates all the ROMs needed for a specific twiddle\_width and number of points.

#### 3.2.5 Control Logic

The control logic for the FFT is simple. A counter is used to switch the butterflies between modes and pick the twiddle factors from the ROMs they are stored in. The counter is  $log_2$  (N)-bits wide. In addition to the clock and reset signals, it uses a load\_enable signal to start. In addition to controlling when the counter starts, it controls how long the FFT runs. The counter is designed to continue counting if the load enable is set to low and the load enable signal was high for at least N clock cycles. This allows the FFT to keep outputting data for which it has the entire waveform. If the load enable is set to low after less than N clock cycles, there will be an error and the FFT will need to be reset.

The FFT takes in a stream of complex numbers. The first clock cycle when the load enable is high is when the first data point is read. On the N-1 clock cycle, the counter is equal to its maximum value, and the output from the FFT is dependent on the input. It takes the output on that clock cycle longer to stabilize than any other clock cycle.

#### 3.2.6 Structure

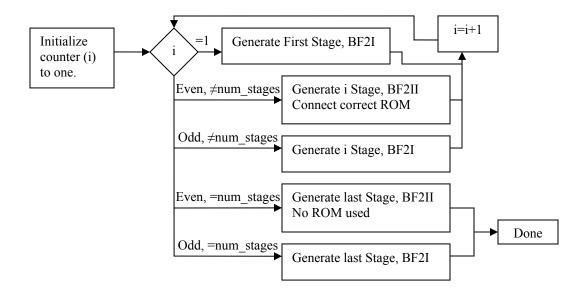

The structure of the FFT is built based on the parameters. The number of points (N) sets how many stages the system will have (num\_stages) to log<sub>2</sub> (N). The bit width of the input is controlled by the input\_width, and how many bits wide the output signal will be is set by the number of stages, the multiplier growth, and the adder growth. Figure 3-7 shows a flowchart of how the structure is generated.

After initializing a counter to one, a generate loop runs from i=1 until i=num\_stages. During each iteration of the loop, several conditional **generates** assign the correct butterfly for that stage and connect the inputs and outputs of the butterfly to the correct signals. The first stage has its inputs connected to the input signal of the FFT. When each stage is generated, it has an input width equal to the following equation. The division of i minus one by two, when

stage width = input width + add

$$g*i + mult$$

$g*((i-1)/2)$  (3)

performed in VHDL, does not return the fractional part of the answer. The equation generates the bit width of the output of the butterfly in each stage. Subtracting add\_g from the equation gives the input width. In the BF2I butterfly, the stage\_width is equal to the output width. In the BF2II butterfly, the output width is equal to stage\_width plus the multiplier growth parameter.

Figure 3-7: Top Level FFT Generation Flow

In order to hold the interconnections, an array of signals is created. The width of the signals in the array is set by the equation above, substituting num\_stages in for i. The number of signals in the array is equal to num\_stages minus one. Only the parts of the signal that are used will be synthesized. For example, if the output width of a stage is 13 bits and the output bitwidth is 36 bits, 23 bits of the array entry that correspond to that stage output are not connected to any signals. Since those signals are not connected to anything, they will not be synthesized. In Pre-synthesis simulation they can still be seen, however

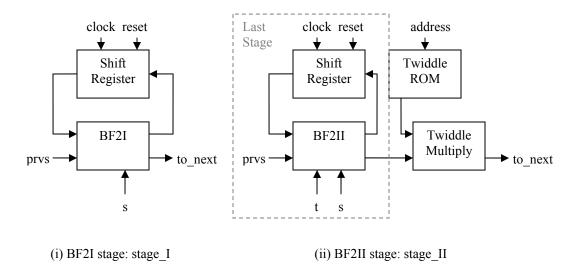

The output from the last stage is connected to the output of the FFT macro. If the last stage is an odd-numbered stage, then the BF2I butterfly is used. If the last stage is an even-numbered stage, the BF2II butterfly is used, but there is no twiddle factor multiplication. Figure 3-8 shows what the structure of each stage looks like. Except for the control signals (clock, reset, address, t, and s), all the signals in the stages are complex. The gray box labeled "Last Stage" in Figure 3-8(ii) shows which components of stage\_II are used in the last stage if it is an even-numbered stage.

The shift registers in Figure 3-8 are actually two shift registers in parallel. One is for the real part of the signal; the other is for the imaginary part. The width of each shift register is stage\_width bits, and the depth is 2<sup>num\_stages-i</sup>. So for the first stage of a 64-point FFT, the shift register is 32 stages deep. The address line controlling the twiddle factor ROM is

Figure 3-8: FFT Stage Structures

num\_stages minus i plus two bits wide. The address line width is equivalent to taking the counter output from the bit tied to t down to zero. So, for the fourth stage in a 64-point FFT, the twiddle factor ROM has 16 entries and the address signal is connected to the lower four bits of the counter (from the t bit down to the lowest bit). The Twiddle Multiply block is a wrapper for the complex multiplier. It contains the complex multiplier and truncates the output of the multiplier to a width equal to the width of the butterfly output plus the multiplier growth.

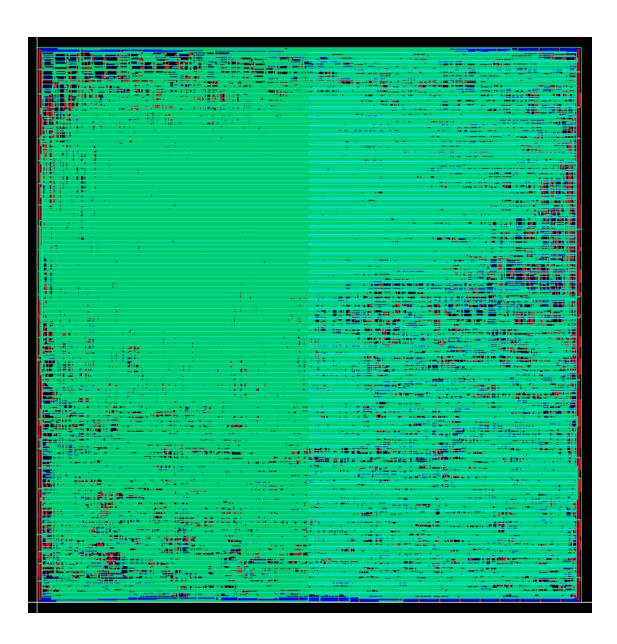

Figure 3-9 is an example of a 64-point FFT. The input width is set to 12 bits, the twiddle width is set to 10, the multiplier growth is set to 9, and the adder growth is set to 1. As with Figure 3-8, all the signals in Figure 3-9 are complex except the control signals. The widths of the signals are labeled, and the widths are for each part of the signal (real and imaginary).

Rather than clutter the figure with the control lines, the output from the counter is labeled. The most significant bit in the counter is labeled c5, and the number decreases to the least significant bit, c0. The control signal s for the first butterfly is tied to c5. The formula for determining which control bit a stage uses is num\_stages-i. The address line of the twiddle factor ROM for the second stage is labeled [c5..c0]. This notation means the most significant bit in the address is tied to the highest bit in the counter, and second most significant bit is tied to the second highest bit, and so on down to the least significant bits of each signal being connected.

Figure 3-9: Generated Structure of 64-point FFT

As was mentioned earlier, on the clock cycle when the last point of data is on the input has the longest delay. On that clock cycle, all the butterflies are in active mode and the complex multipliers are operating along the path. By tracing the data path through Figure 3-8, the amount and type of operations can be seen. The data must travel through six addition or subtraction operations and two complex multiply operations. As the number of points grows, the number of multipliers and additions/subtractions increases, which increases the delay. For a 1024-point FFT, the data will travel through ten addition/subtraction operations and four complex multiply operations. Increasing the bit-width of the input or the twiddle factor will also increase the delay, because the arithmetic operations take longer to reach an answer for larger inputs. Controlling the growth of the signal is the purpose of the mult\_g parameter. By decreasing the mult\_g parameter, the growth of the signals will be smaller, which will translate to less delay. However, truncating the output of the multiplier will decrease the accuracy of the results.

The VHDL files included are configured to match the parameters in this example. The hierarchy for the VHDL macros is functionally equivalent to what is presented here. The generate loop shown in Figure 3-7 is in the top-level module fft\_core.vhd. This loop connects the different types of stages (stage\_I.vhd, stage\_II.vhd, stage\_II.vhd, stage\_II.vhd, and stage\_II\_last.vhd) together. The only difference between stage\_I.vhd and stage\_I\_last.vhd is that stage\_I.vhd uses shiftregN.vhd to instantiate the shift registers, and stage\_I\_last.vhd uses shiftreg1.vhd for its 1-stage shift registers. The even-numbered stages that are not the last stage are implemented using stage\_II.vhd. This module contains the BF2II butterfly (BF2II.vhd), two copies of the shiftregN macro, and the twiddle multiplier (twiddle\_mult.vhd). It has inputs that are wired to the twiddle factor ROM for that stage. The ROMs are numbered from largest to smallest, so the first ROM in the data path is always rom1.vhd. The other type of stage II module, stage\_II\_last.vhd, is identical to the stage\_II.vhd module, except that it does not include the complex multiplier or the inputs from the ROM.

#### 3.2.7 Test Bench

The test bench for the FFT is written in VHDL, but it loads test vectors that are created in MATLAB. The vectors control the FFT and send three input waveforms into it. The second vector is repeated as the third, and the only purpose for it is to enable the test bench to keep writing the output of the second waveform until it finishes. After the clock is started, the test

bench writes the output of the FFT to a file. By default, it reads from a file called "testvec" and writes to a file called "data.out".

The test vectors generated are a concatenation of the reset, load\_enable, xin\_r (the real part of the input), and xin\_i (the imaginary part of the input). In the files the bits of the signals are ASCII characters, not stored binary numbers. This makes it easy for a user to examine the files and verify that they have been generated correctly. By putting the reset and load\_enable into the test vectors, the only signal that needs to be set in the test bench is the clock. However, having the reset operating at almost the same time as the clock can cause problems in simulations after synthesis. In this case, it is better to force the reset signal high during the clock cycle before the reset would be set high by the test bench.

The advantage of writing the vectors in MATLAB is that creating an approximate model of the FFT is easy. After the test bench has been simulated, a second MATLAB file, plotdata.m, can read the original test vectors, convert them to floating point numbers, perform MATLAB's built in FFT function on them, and finally plot them and the results of the FFT simulation. This allows for easy visual comparison of the outputs. It can be modified to display data in different ways (real and imaginary or magnitude and phase), depending on what test vectors are input. If the Pre-synthesis results are correct, a new test bench can be created to read the Pre-synthesis results and compare them to the FFT being simulated.

In addition to a MATLAB test bench, a BIST module for the 64-point FFT has been created. This module operates as was described in section 2.4.3. The purpose of this module is to serve as an inexpensive alternative to external testing hardware. It is not reconfigurable at this time, but the components except for the ROM are.

# **Chapter 4: Results**

#### 4.1 Rounders

The test bench for each rounder module instantiates the macro under test, sets up an internal clock, and then inputs the test vectors into the macro. Each macro had over 1000 test vectors. The q\_out signal is compared to the expected\_q\_out signal each clock cycle, and if they were not equal, an error is reported. The parameters in each simulation are displayed as integers, the control signals (if any) as binary numbers, and the data signals as hexadecimal numbers. When referring to binary numbers, 0b will be before the number. Hexadecimal numbers in text will have 0x in front of them. Due to the length of the rounder test benches, they are not included in the Appendices.

#### 4.1.1 Fixed Rounder

Figure 4-1 shows a sample of the Fixed Rounder simulation. The figure shows five test vector inputs and outputs. This is a Pre-synthesis simulation, so the outputs appear to be changing at the same time as the input. This is an effect of using a Δ delay in an event driven simulation. In this simulation, there are no input or output registers (ri and ro are equal to zero); the input d\_in is a 23-bit wide signal. The rounding is set to be on the 10<sup>th</sup> bit, and the final output width is set to 12 bits. This means the output from the rounding section (rounded) will be clipped down to 12 bits from 13.

The last input shown, 0x5652C7, is an example of a negative number that is too large to fit in a 12-bit number, so the output is set to the maximum 12-bit signed number, 0x801. The second and fourth test vectors are both positive numbers that are too bit to fit in a 12-bit number, so the output is set to 0x7FF, the maximum positive output. The 10<sup>th</sup> bit of the first test vector is one, so that test vector shows a successful positive round. The 10<sup>th</sup> bit of the third test vector is a zero, so that vector shows a case where a positive number is not rounded.

Initially, one test case was missed in the test vectors. In the clipping section, it was possible for a negative number to be set to outside the intended range of outputs. For example, if the input was 0b111000, the rounding position was set to zero, and the output width set to 5, the Fixed Rounder would return 0b1000, instead of the intended 0b1001. The code was modified to account for this case, the test vector added to the test bench, and the Fixed Rounder was successfully simulated for all the test vectors.

Figure 4-1: Sample of Fixed Rounder Test Bench Simulation

## 4.1.2 Configurable Rounder

Figure 4-2 shows a sample of the test bench simulation for the Configurable Rounder. The test bench sets the input width to 23, the output width to 12, the rounder select width to 4, and the radix position (cr\_rad\_pos) to 11. It also instantiates a pipeline register on the output by setting ro to one. The pipeline register is set to a synchronous reset by setting rt to one. The out\_load\_enable signal shown is not used, because the output register is not set to two. Since there is a register on the output, the q\_out shown is the rounded output for the previous input. It should be noted that the Fixed Rounder block used in this simulation has different parameters than the Fixed Rounder in the previous simulation.

The ext\_d\_in signal shown is the array that is created in the configurable rounder. In the figure, it is broken down into its four component signals, labeled (0) to (3). Entry (0) corresponds to the signal in Figure 3-2 that is just sign extended, and (3) corresponds to the signal that is just padded.

The Configurable Rounder simulated correctly for all input vectors.

## 4.1.3 Output Gain Stage

Figure 4-3 shows part of the test bench simulation for the Output Gain Stage. The parameters controlling the width are displayed in the simulation. Because of the number of parameters in this design, the parameters controlling the insertion of registers were left off the simulation output. In this test bench ri, ro, rc, pr, and rt are all set to one. This will insert a pipeline register with a synchronous reset on the inputs d\_in, cr\_rndr\_sel, and gain. A pipeline register will be inserted between the Configurable Rounder instantiation and the multiplier, and on the output of the fixed rounder. This leads to a complicated data flow. For example, the fifth q\_out\_in Figure 4-3 is 0x0F6. The d\_in\_and cr\_rndr\_sel\_used to calculate this answer are 0x0004EE0 and 0b011, which are input to the system three clock cycles before the output is ready.

The Configurable Rounder block used in this simulation has different parameters than the macro used in the previous simulation. The Fixed Rounder inside the Configurable Rounder has different parameters than the two used in previous simulations. The second Fixed Rounder in this simulation has the same parameters as the first Fixed Rounder simulation, except ro is set to one.

The Output Gain Stage simulated correctly for all test vectors.

Figure 4-2: Sample of Configurable Rounder Test Bench Simulation

Figure 4-3: Sample of Output Gain Stage Test Bench Simulation

#### 4.2 FFT Results

The simulations in this section were run using the test bench described in section 3.2.7. MATLAB was used to create the test vectors, and the same test vectors are used in all the simulations where N is equal to 64. Except for the section covering FFT results from different numbers of inputs, all the simulations are using a 64-point FFT.

#### 4.2.1 *MATLAB*

MATLAB is used to generate the test vectors and to compare the outputs to what MATLAB calculates them to be. The test vectors that are generated by default are a sinc wave followed by a square wave. These are used because in the frequency domain they change from one to another. So the FFT of the sinc wave is a square wave, and the FFT of a square wave is a sync wave.

All the simulations in the following sections use the same formulas to determine the test vectors. The Sinc Wave input uses sinc((x-N/2)/2), and the square wave has a duty cycle of 0.125.

## 4.2.2 Pre-synthesis and Pre-layout

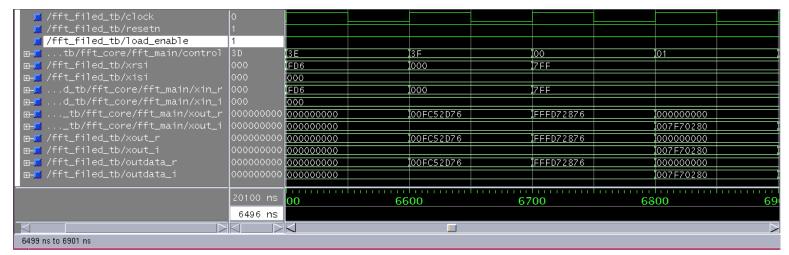

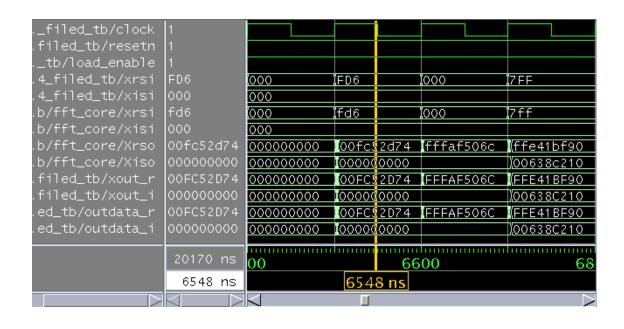

Figure 4-4 shows a comparison of the same clock cycles for the Pre-synthesis simulation and the pre-layout simulation. Figure 4-4(i) shows the Pre-synthesis simulation. This simulation is event driven and is using a  $\Delta$  delay. Figure 4-4(ii) shows the pre-layout simulation, and is using a fixed delay of 1 ns per gate and is also event driven. Due to some timing issues with how the test bench writes the data out (it writes to the file on the falling edge), the pre-layout simulation is using a clock with a 200 ns period, while the Pre-synthesis is using a 100 ns clock period. The figures are showing the waveforms near the clock cycle at the end of the first input vector. The control signal in Figure 4-4(i) shows the value of the counter in the main FFT.